Silicon photonics has gained significant importance in data centers in recent years, enabling fast and efficient connections between switches, servers, and other equipment over long distances using the power of photons. As the demand for bandwidth continues to rise, silicon photonics is expected to play an even more crucial role. Imec, a leading semiconductor research lab, predicts that silicon photonics will be responsible for chip-to-chip connectivity between CPUs, GPUs, and other XPUs in data centers and AI supercomputers.

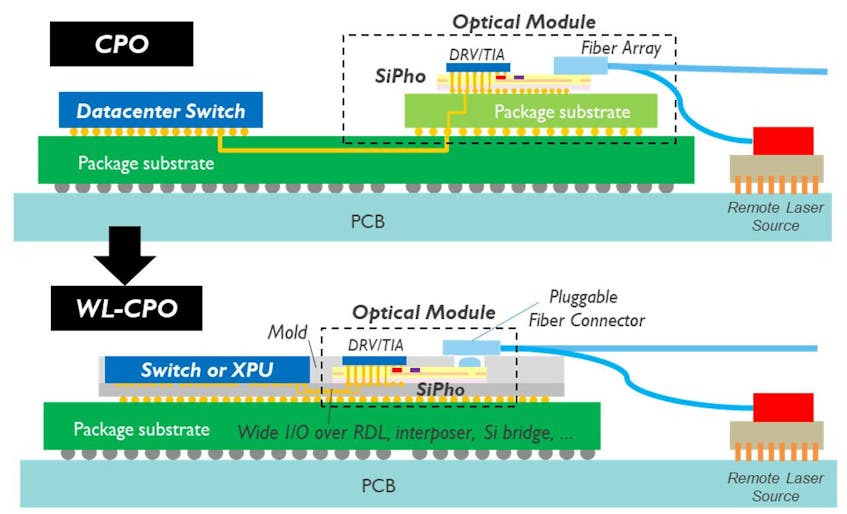

Integrating optics and electronics closely is a significant challenge, but the semiconductor industry is actively working on addressing this challenge. The development of a new generation of switch chips with co-packaged optics is evidence of the industry's effort in this regard.

Imec aims to enhance the power efficiency, bandwidth density, and cost of silicon photonics by an order of magnitude over time. This would enable the adoption of more advanced co-packaged optics called "wafer-level optical interconnects," which can transfer data between chips on a printed circuit board (PCB) or inside a package at the speed of light.

Imec has been at the forefront of advancing silicon photonics, developing various electro-optical components based on silicon and germanium with bandwidths of up to 50 GHz. They have also overcome integration challenges, such as integrating lasers, waveguides, and other optical building blocks. Imec has accomplished this by integrating low-pressure chemical vapor deposition (LPCVD)-based SiN waveguides and developing SiPho interfaces for flip-chip-based laser integration. Additionally, they are exploring the integration of "exotic" electro-optic materials into the silicon photonics process to achieve higher bandwidths.

The need for high-bandwidth optical interconnect networks extends beyond data centers. With the rise of large generative AI models, networking bandwidth has become critical for high-performance AI/ML clusters. Pluggable optical interconnects are already replacing copper interconnects within computer clusters, but as these clusters scale, optical interconnects will move into the board and package to meet interconnect bandwidth requirements. This shift places added pressure on metrics like bandwidth density, power consumption, cost, and reliability. High-bandwidth optical transceivers with low power consumption, low latency, and high reliability at an affordable cost will be needed.

Imec is addressing these challenges by scaling bandwidth using a larger number of parallel optical channels optimized for efficiency rather than overall bandwidth. They are also exploring wafer-level co-packaged optics and leveraging advanced packaging technologies like micro bumps, through-silicon vias (TSVs), silicon bridges, and hybrid bonding. Power-efficient electrical wide-I/O interfaces are used for shorter-range copper interconnects, and the integration of light sources onto SiPho chips is being pursued to enhance cost and optical link budgets.

Recent research efforts at imec have focused on optimizing silicon ring modulators, WDM filters, and circuits to enable low-power hybrid CMOS-SiPho transceivers. They have achieved remarkable results with ring-based CMOS-SiPho transceivers that consume as little as 3.5 pJ/bit of optical energy and have extremely low bit error rates. Imec is also working on improving yield through wafer-scale solutions for known-good die testing of SiPho transceivers.

Looking ahead, imec envisions wafer-level co-packaged optics combined with aggressive WDM as a way to achieve fiber-coupled optical links with bandwidth densities of 2-4 Tb/s per mm at low power consumption. In the long term, optical interconnects approaching 10 Tb/s per mm of bandwidth density and power consumption below 1 pJ per bit are expected. Imec is exploring wafer-level optical interconnects for ultra-high-bandwidth chip-to-chip optical I/O, which could revolutionize system performance by enabling massively parallel, optical XPU-to-XPU connectivity.

Imec's extensive in-house expertise in silicon photonics and CMOS integration, along with their collaboration with partners and access to diverse competencies, greatly contributes to their optics research. They leverage decades of experience in silicon photonics development and 3D integration technologies. Imec's system-technology co-optimization (STCO) team supports the system-level analysis required for the integration of optical interconnects. This collective expertise enables the development of complex systems and technologies to meet the evolving demands of data centers and AI/ML clusters.