Imec, a Belgian research institute, has announced a roadmap for the development of sub-1nm chips. Though typical transistor counts are predicted to double, as part of Moore's Law, imec rather argues that raw computing power for AI and ML doubles once every six months.

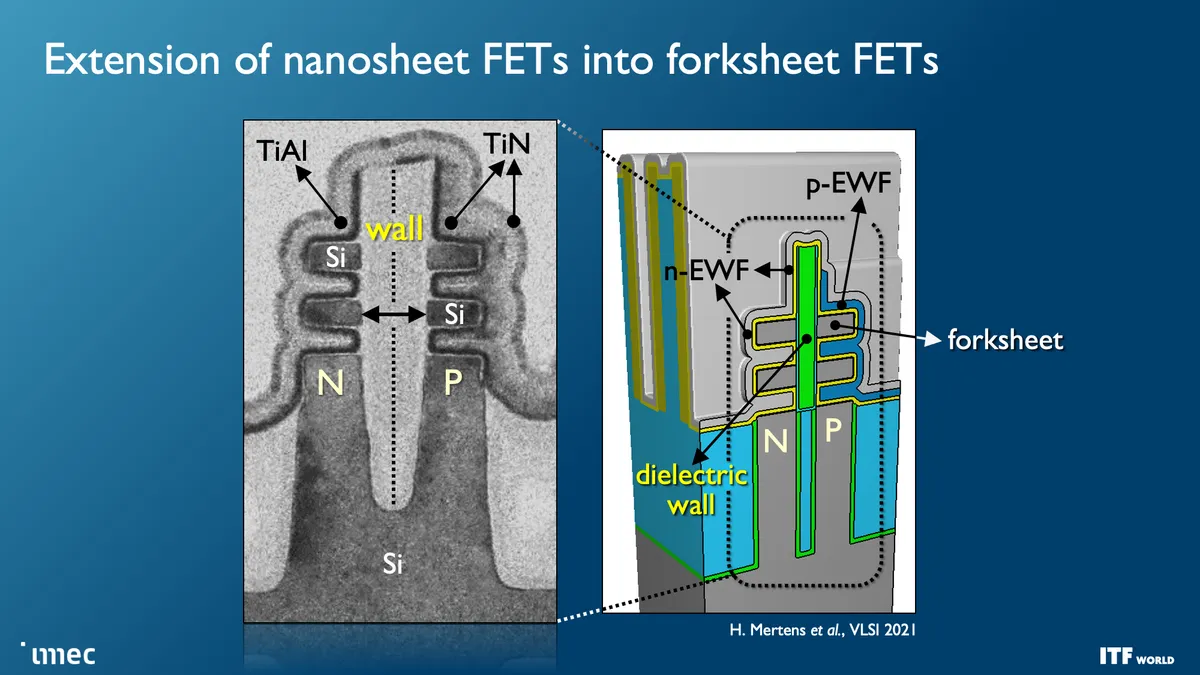

The proposed roadmap features several unique chip designs and technologies, including gene all around (GAA) nanosheet manufacturing, fork-sheet and complementary FET (CFET) transistor, and backside power delivery networks. Additionally, there is an intention to use complementary metal-oxide-semiconductor (CMOS) 2.0 technology to divide chips into smaller pieces while stacking units that use different transistors to establish 3D arrangements. The roadmap proposes a continuous reduction in interconnect size and 3D stacking chip designs to create sub-1nm silicon. However, there's the issue that interconnect bandwidth limitations severely lag behind computational capabilities and could limit the effectiveness of new technologies. Sub-1nm processing power is expected to revolutionise the semiconductor industry and enhance the capabilities of AI and other machine learning devices.