Imec, a prominent research and innovation hub in digital technologies and nanoelectronics, revealed at the 2023 IEEE International Interconnect Technology Conference that it has discovered evidence of the resistivity of a thin conductor film on a 300mm Si wafer that is lower than that of Cu and Ru.

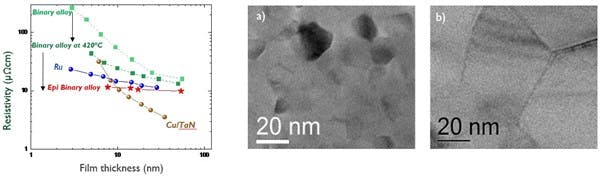

For example, a low resistance of 11.5µWcm was measured for a NiAl binary alloy of 7.7nm thickness that was obtained after grain size engineering. This marks an important milestone towards enabling low-resistance interconnects with line widths that are lower than 10nm. Currently, state-of-the-art memory and logic chips rely on interconnects with widths are below 10nm. Copper, which is commonly used in metallization schemes, experiences a significant increase in resistivity at these small dimensions, and its reliability degrades over time. To address these challenges, researchers have sought alternatives to Cu metallization, such as elemental metals and binary and ternary ordered intermetallics. Imec used a unique ab-initio-based selection methodology that ranks materials based on their bulk resistivity and mean free path of carriers (r0 x l) as a key metric. Theoretical assessments were followed by experimental investigations on 300mm wafers. Resulting experimental evidence of low-resistive thin conductor films on 300mm wafers paves the way for future research on binary and ternary alloys with an emphasis on composition control and compatibility with metallization schemes.

Source: IMEC